USE DISCOUNT CODEEXPERT30TO SAVE $30 USD

Impedance control on PCBs

andras_t , 09-11-2020, 05:53 AM

Dear Members!

I would like to ask your opinion about impedance control on PCBs. I am hardware developer and I design high speed PCBs at a big company where we have more high speed interfaces on the boards, like oLDI, HDMI, FPD link, APIX, LPDDR4, MIPI CSI etc. Until now we did not use impedance control on our PCB-s. Our maximum datarate is currently 3Gbit/s.

I think that impedance control is very important but most of my colleagues say that until now there were no problems then why should we use...

What is the border where we should begin to use impedance controlled pcb-s? Do you know with what kind of tolerance pcb manufacturers work with and without impedance control?

I know that these problems could occur:

- video distortions (pixel errors and synchronization gaps)

-- data interfaces will have transfer gaps, bit errors

-- DRAM errors

-- significant increased EMC (impedance jump -> causes reflections -> causes emissions)

-- Impedance jump from Chip-out to trace and on Board-to-Board routings

The problem is that I have never seen such problems in our projects (we sell from one product 300-400 thousand pieces / year) and I do not know how I could prove that without impedance control we are bad.

And we use higher and higher datarates. For example we use in our new projects LPDDR4 instead of DDR3, where we have instead of 533MHz a clock frequency of 1600 MHz, so rise and fall times are also much shorter. That's why I am thinking that maybe the time has come to use impedance control

What do you think about this topic?

Thank you for your answers in advance!

best regards,

Andras

I would like to ask your opinion about impedance control on PCBs. I am hardware developer and I design high speed PCBs at a big company where we have more high speed interfaces on the boards, like oLDI, HDMI, FPD link, APIX, LPDDR4, MIPI CSI etc. Until now we did not use impedance control on our PCB-s. Our maximum datarate is currently 3Gbit/s.

I think that impedance control is very important but most of my colleagues say that until now there were no problems then why should we use...

What is the border where we should begin to use impedance controlled pcb-s? Do you know with what kind of tolerance pcb manufacturers work with and without impedance control?

I know that these problems could occur:

- video distortions (pixel errors and synchronization gaps)

-- data interfaces will have transfer gaps, bit errors

-- DRAM errors

-- significant increased EMC (impedance jump -> causes reflections -> causes emissions)

-- Impedance jump from Chip-out to trace and on Board-to-Board routings

The problem is that I have never seen such problems in our projects (we sell from one product 300-400 thousand pieces / year) and I do not know how I could prove that without impedance control we are bad.

And we use higher and higher datarates. For example we use in our new projects LPDDR4 instead of DDR3, where we have instead of 533MHz a clock frequency of 1600 MHz, so rise and fall times are also much shorter. That's why I am thinking that maybe the time has come to use impedance control

What do you think about this topic?

Thank you for your answers in advance!

best regards,

Andras

Lakshmi , 09-11-2020, 07:37 AM

Hi,

Was the PCB's designed by you? OR You're a part of the hardware design team?

I hope the below-attached links cover some of your questions :

Manufacturer's usually keeping a tolerance of +/- 10%.

Was the PCB's designed by you? OR You're a part of the hardware design team?

I hope the below-attached links cover some of your questions :

Manufacturer's usually keeping a tolerance of +/- 10%.

robertferanec , 09-12-2020, 03:23 AM

@andras_t that is very interesting! I will ask others what they think about it. Maybe your boards are small or the impedance of tracks is still close around 50OHMs? What I would be more interesting to know, if they do not care about impedance, does it mean, they do not care about stackup? And what about length matching?

PS: Personally I would go for impedance controlled PCB. I always try to design as good as possible.

PSS: When something is wrong, most of the failing I have seen were visible:

- in the environmental chamber (when temperatures were changing)

- in burn in test (when whole board was running under a very high stress tests - all interfaces running at full speeds and loads)

- in long run test (boards running for months)

PS: Personally I would go for impedance controlled PCB. I always try to design as good as possible.

PSS: When something is wrong, most of the failing I have seen were visible:

- in the environmental chamber (when temperatures were changing)

- in burn in test (when whole board was running under a very high stress tests - all interfaces running at full speeds and loads)

- in long run test (boards running for months)

qdrives , 09-12-2020, 07:09 AM

In theory I would say that if you know the (estimate) the final thickness of the prepreg and core layers, you could calculate the trace width.

andras_t , 11-02-2020, 07:04 AM

Dear All,

Thank you for your answers. We perform a lot of tests (I work in a very big company) like humidity tests, lot of tests in thermal chamber, EMC, so everything you can imagine. Until now in our previous projects we used DDR3 interface with max 1066MBit/s and in this case we did not have problems with PCBs without impedance control.

We have some 3Gbit/sec interfaces but those signal lines were very short and we could never test with the device connected to it to check signal integrity (the other device is from other automotive supplier and we can not get them).

To asnwer some of your questions:

We have quite big PCBs: now we have a PCB of: 260mm x 100mm

Now we use impedance designed PCBs: we design the traces to have a specific impedance but without impedance control nobody guarantees that it is really e.g 85 Ohm +-10%. We measured with TDR and without impedance control the impedance for a 85Ohm trace is somewhere between 70 Ohm and 100 Ohm, you can never know what you get. I have seen big differences between suppliers too.

We use length matching in every projects (which I support)

We consider also layer stackups at the beginning of all of our projects

But in our new projects we moved to LPDDR4 to a datarate of 3,2Gbit/sec, and I have the feeling that we reached the point where we should begin to use impedance controlled PCBs. But it is difficult to convince managers, because it costs money. That's why I asked you to collect some ideas how could I convince our managers. Now the decision is that we wait until we have a big problem and we can we exciting task forces and we can work again on saturdays

I would go also for impedance controlled PCBs, I fully agree with you. I know Eric Bogatin and Rick Hartley, I have seen many videos from them.

Thank you again

Thank you for your answers. We perform a lot of tests (I work in a very big company) like humidity tests, lot of tests in thermal chamber, EMC, so everything you can imagine. Until now in our previous projects we used DDR3 interface with max 1066MBit/s and in this case we did not have problems with PCBs without impedance control.

We have some 3Gbit/sec interfaces but those signal lines were very short and we could never test with the device connected to it to check signal integrity (the other device is from other automotive supplier and we can not get them).

To asnwer some of your questions:

We have quite big PCBs: now we have a PCB of: 260mm x 100mm

Now we use impedance designed PCBs: we design the traces to have a specific impedance but without impedance control nobody guarantees that it is really e.g 85 Ohm +-10%. We measured with TDR and without impedance control the impedance for a 85Ohm trace is somewhere between 70 Ohm and 100 Ohm, you can never know what you get. I have seen big differences between suppliers too.

We use length matching in every projects (which I support)

We consider also layer stackups at the beginning of all of our projects

But in our new projects we moved to LPDDR4 to a datarate of 3,2Gbit/sec, and I have the feeling that we reached the point where we should begin to use impedance controlled PCBs. But it is difficult to convince managers, because it costs money. That's why I asked you to collect some ideas how could I convince our managers. Now the decision is that we wait until we have a big problem and we can we exciting task forces and we can work again on saturdays

I would go also for impedance controlled PCBs, I fully agree with you. I know Eric Bogatin and Rick Hartley, I have seen many videos from them.

Thank you again

robertferanec , 11-06-2020, 03:13 AM

I am not sure how to convince managers - maybe they will listen when something doesn't work.

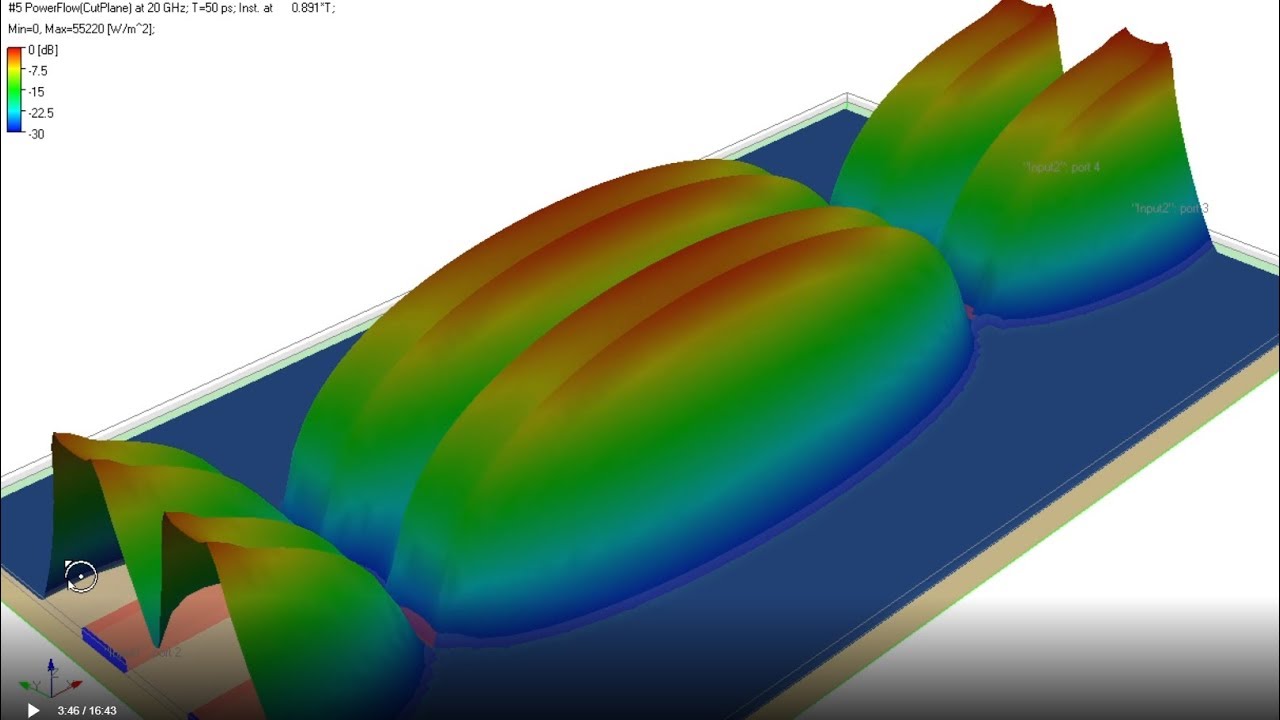

Just yesterday I posted a video where I told, that maybe up to 3-5 GHz it is still possible to go away with problems even if PCB layout is not perfect. But above 5-10GHz it really looks like everything is becoming important, not only impedance, but also every single via and track: https://youtu.be/vzqZm2IFn6Y

We are currently working on LPDDR4 3200 and I am thinking to make some videos about simulating that interface. That could help to understand how sensitive it is. But I am not sure when the video will come out (and if).

Just yesterday I posted a video where I told, that maybe up to 3-5 GHz it is still possible to go away with problems even if PCB layout is not perfect. But above 5-10GHz it really looks like everything is becoming important, not only impedance, but also every single via and track: https://youtu.be/vzqZm2IFn6Y

We are currently working on LPDDR4 3200 and I am thinking to make some videos about simulating that interface. That could help to understand how sensitive it is. But I am not sure when the video will come out (and if).

qdrives , 11-11-2020, 04:01 PM

@andras_t You should have signed in for the EMI webinar of Rick Hartley that is busy now. When the clock rate rises, the rise times of the signals drop. With faster rise times the trace length where it does not matter become shorter. In your old design 40mm may have been ok, but with the new design this may have dropped to 15mm (I do not know the details exactly).

1066 DDR(3) is 533MHz, 3.2GB DDR4 is 1.6GHz or 3x the speed.

Formula was that if the length is below 1/4 propagation of the rise time, no problem. Above that -> a transmission line.

1066 DDR(3) is 533MHz, 3.2GB DDR4 is 1.6GHz or 3x the speed.

Formula was that if the length is below 1/4 propagation of the rise time, no problem. Above that -> a transmission line.

Use our interactive Discord forum to reply or ask new questions.